Latches, Flip-Flop and Pewaktu (Timer) x

Latches

The output of a latch depends on its current inputs and on its previous output and its change of state can happen at any time when its inputs change Program Studi T. Elektro FT - UHAMKA Slide - 8 2 The output of a latch depends on its current inputs and on its previous output and its change of state can happen at any time when its inputs change

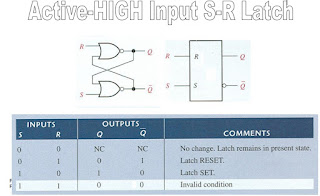

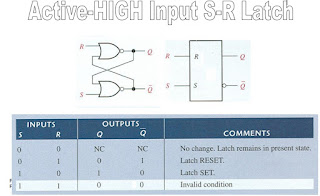

S-R (Set-Reset) Latch

Gated S-R Latch

Gated D Latch

S-R Latch

Negative-OR Equivalent of the NAND gate /S-/R Latch

Example: Determine the waveform that will be observed on the Q output. Assume that Q is initially LOW

The Gated S-R Latch A gated latch requires an Enable input, EN (G is also used to designated an enable input). The S and R inputs control the state to which the latch will go when a HIGH level is applied to the EN input. The latch will not change until EN is HIGH.

Truth Table for Gated S-R Latch

The Gated D Latch Only has one input in addition to EN. This input is called the D (data) input. -When the D input is HIGH and the EN input is HIGH, the latch will SET. -When the D input is LOW and EN is HIGH, the latch will RESET. -Another way, the output Q follows the input D when EN is HIGH

Edge-Triggered Flip-Flops

Edge-triggered S-R flip-flop

Edge-triggered D flip-flop

Edge-triggered J-K flip-flop

Edge-Triggered Flip-Flop Logic Symbols (Top: Positive Edge-Triggered; Bottom: Negative Edge-Triggered).

The Edge-Triggered S-R Flip-Flop The S and R inputs of the S-R flip-flop are called synchronous input because data on these inputs are transferred to the flip-flop’s output only on the triggering edge of the clock pulse.

Operation of a positive edge-triggered S-R flip-flop

Example: Determine the Q and /Q output waveforms of the flip-flop (Assume is initially RESET)

Exercise: Determine the Q and /Q output waveforms of the flip-flop (Assume is initially RESET) and it is a negative edge-triggered device

The Edge-Triggered D FlipFlop The D flip-flop is useful when a single data bit (1 or 0) is to be stored

source : https://onlinelearning.uhamka.ac.id/

S-R (Set-Reset) Latch

Gated S-R Latch

Gated D Latch

S-R Latch

Negative-OR Equivalent of the NAND gate /S-/R Latch

Example: Determine the waveform that will be observed on the Q output. Assume that Q is initially LOW

The Gated S-R Latch A gated latch requires an Enable input, EN (G is also used to designated an enable input). The S and R inputs control the state to which the latch will go when a HIGH level is applied to the EN input. The latch will not change until EN is HIGH.

Truth Table for Gated S-R Latch

The Gated D Latch Only has one input in addition to EN. This input is called the D (data) input. -When the D input is HIGH and the EN input is HIGH, the latch will SET. -When the D input is LOW and EN is HIGH, the latch will RESET. -Another way, the output Q follows the input D when EN is HIGH

Edge-Triggered Flip-Flops

Edge-triggered S-R flip-flop

Edge-triggered D flip-flop

Edge-triggered J-K flip-flop

Edge-Triggered Flip-Flop Logic Symbols (Top: Positive Edge-Triggered; Bottom: Negative Edge-Triggered).

The Edge-Triggered S-R Flip-Flop The S and R inputs of the S-R flip-flop are called synchronous input because data on these inputs are transferred to the flip-flop’s output only on the triggering edge of the clock pulse.

Operation of a positive edge-triggered S-R flip-flop

Example: Determine the Q and /Q output waveforms of the flip-flop (Assume is initially RESET)

Exercise: Determine the Q and /Q output waveforms of the flip-flop (Assume is initially RESET) and it is a negative edge-triggered device

The Edge-Triggered D FlipFlop The D flip-flop is useful when a single data bit (1 or 0) is to be stored

source : https://onlinelearning.uhamka.ac.id/

Comments

Post a Comment